# Microprocessor Applications

XMEGA: USART

UF FLORIDA

### USART on the ATxmega128A1U

- The XMEGA has a total of eight Universal Synchronous and Asynchronous Receiver/Transmitter (USART) modules.

- Each module can be configured to perform either synchronous or asynchronous serial communication.

- In this presentation, the synchronous portion will not be covered. More details about it can be found in the XMEGA AU (doc8331) manual.

3

### Alternate Pin Function Table

- Section 33.2 of doc8385 has a table of alternate pin functions for each port.

- ✤ The table for Port C is shown here. See the two columns labeled USARTC0 and USARTC1.

| PORT C | PIN# | INTERRUPT  | TCC0 <sup>(1)(2)</sup> | AWEXC  | TCC1 | USARTC0 <sup>(3)</sup> | USARTC1 | SPIC <sup>(4)</sup> | тwic | CLOCKOUT <sup>(5)</sup> | EVENTOUT <sup>(6)</sup> |

|--------|------|------------|------------------------|--------|------|------------------------|---------|---------------------|------|-------------------------|-------------------------|

| GND    | 13   |            |                        |        |      |                        |         |                     |      |                         |                         |

| vcc    | 14   |            |                        |        |      |                        |         |                     |      |                         |                         |

| PC0    | 15   |            |                        |        |      |                        |         |                     |      |                         |                         |

| PC1    | 16   |            |                        |        |      | XCK0                   |         |                     |      |                         |                         |

| PC2    | 17   | SYNC/ASYNC | OCOC                   | OCOBLS |      | RXD0                   |         |                     |      |                         |                         |

| PC3    | 18   | SYNC       | OCOD                   | OC0BHS |      | TXD0                   |         |                     |      |                         |                         |

| PC4    | 19   | SYNC       |                        | OCOCLS | OC1A |                        |         | SS                  |      |                         |                         |

| PC5    | 20   |            |                        |        |      |                        | XCK1    | MOSI                |      |                         |                         |

| PC6    | 21   | SYNC       |                        | OCODLS |      |                        | RXD1    | MISO                |      |                         |                         |

| PC7    | 22   |            |                        | OCODHS |      |                        | TXD1    | SCK                 |      | CIKPER                  |                         |

UF FLORIDA

Dr. Eric Schwartz | Christopher Crary | Wesley Pia

Table 33-3

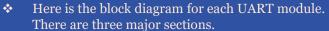

### **Block Diagram**

- The Clock Generator section generates the clock signals required for the *Transmitter* and *Receiver* sections to function properly.

- The Transmitter section shifts data out via the TxD (transmit) pin at the baud rate.

- The **Receiver** section samples data via the RxD (receive) pin.

5

UF FLORIDA

### **UART Clock Generation**

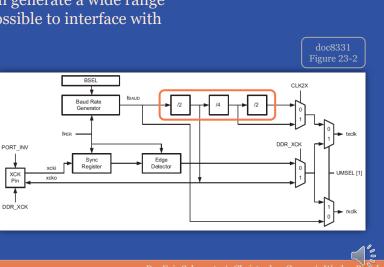

The *Clock Generation* section contains a fractional \*\* baud rate generator that uses the XMEGA's peripheral clock frequency,  $f_{PER}$ , to generate the baud rate,  $f_{BAUD}$ . Figure 23-2  $f_{PER}$  is the frequency of the ••• peripheral clock, clk<sub>PER</sub>, CI K2X which is derived from the Baud Rate Generator overall system clock, clk<sub>sys</sub>. PORT\_INV Edge Sync IMSEL [1] XCK Pin DDR XCH

Dr. Eric Schwartz | Christopher Crary | Wesley Piard

### **UART Clock Generator**

- The UART clock generator can generate a wide range of baud rates such that it is possible to interface with external UARTs.

- Note that the receiver's clock is 16 times faster than the transmitter's clock.

- More details about why this is necessary can be found in section 23.8 of the doc8331 manual.

UF FLORIDA

7

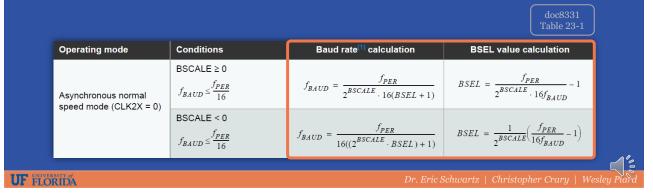

# UART Clock Generator – Baud Rate Equations

- ◆ To configure a UART for a specific baud rate, the equations below are utilized.

- The three parameters that can be modified are  $f_{PER}$ , BSEL, and BSCALE.

- ★ The equations that calculate  $f_{BAUD}$  (in the third column) are equivalent to the equations used to calculate *BSEL* (in the fourth column). The only difference is which parameter is solved for.

- Note that the CLK2X bit can be set to allow for higher baud rates. See the rest of Table 23-1 in the doc8331 manual for more details.

Table 23-1

| perating mode                               | Conditions                                                                          | Baud rate <sup>(1)</sup> calculation                         | BSEL value calculation                                                       |

|---------------------------------------------|-------------------------------------------------------------------------------------|--------------------------------------------------------------|------------------------------------------------------------------------------|

| synchronous normal<br>peed mode (CLK2X = 0) | $\begin{aligned} BSCALE &\geq 0 \\ f_{BAUD} &\leq \frac{f_{PER}}{16} \end{aligned}$ | $f_{BAUD} = \frac{f_{PER}}{2^{BSCALE} \cdot 16(BSEL + 1)}$   | $BSEL = \frac{f_{PER}}{2^{BSCALE} \cdot 16f_{BAUD}} - 1$                     |

| peed mode (CER2X = 0)                       | $\begin{split} & BSCALE < 0 \\ & f_{BAUD} \leq \frac{f_{PER}}{16} \end{split}$      | $f_{BAUD} = \frac{f_{PER}}{16((2^{BSCALE} \cdot BSEL) + 1)}$ | $BSEL = \frac{1}{2^{BSCALE}} \left( \frac{f_{PER}}{16 f_{BAUD}} - 1 \right)$ |

#### UF FLORIDA

Dr. Eric Schwartz | Christopher Crary | Wesley Piar

### UART Clock Generator – Baud Rate Equations

- ★ The baud rate generated,  $f_{BAUD}$ , is determined by the period setting, *BSEL*, an optional scale setting *BSCALE*, and the peripheral clock frequency  $f_{PER}$ .

- Generally, the first step when configuring UART is to determine the baud rate. The two UARTs that are communicating must have identical, or as close to identical as possible, baud rates.

|                                               |                                                                                           |                                                              | Table 23-1                                                                   |

|-----------------------------------------------|-------------------------------------------------------------------------------------------|--------------------------------------------------------------|------------------------------------------------------------------------------|

| Operating mode                                | Conditions                                                                                | Baud rate <sup>(1)</sup> calculation                         | BSEL value calculation                                                       |

| Asynchronous normal<br>speed mode (CLK2X = 0) | $\begin{aligned} BSCALE &\geq 0 \\ f_{BAUD} \leq \frac{f_{PER}}{16} \end{aligned}$        | $f_{BAUD} = \frac{f_{PER}}{2^{BSCALE} \cdot 16(BSEL + 1)}$   | $BSEL = \frac{f_{PER}}{2^{BSCALE} \cdot 16f_{BAUD}} - 1$                     |

|                                               | $\begin{aligned} & \text{BSCALE < 0} \\ & f_{BAUD} \leq \frac{f_{PER}}{16} \end{aligned}$ | $f_{BAUD} = \frac{f_{PER}}{16((2^{BSCALE} \cdot BSEL) + 1)}$ | $BSEL = \frac{1}{2^{BSCALE}} \left( \frac{f_{PER}}{16 f_{BAUD}} - 1 \right)$ |

|                                               |                                                                                           | Dr. Eric S                                                   | Schwartz   Christopher Crary   Wes                                           |

9

UF

### UART Clock Generator – Baud Rate Equations

• For a given  $f_{BAUD}$ , the following values must be chosen or calculated:

$f_{PER}$  : 2 MHz by default for the XMEGA; derived from the system clock

- ▶ *BSEL* : Period value between 0 and 4095

- > BSCALE : A value in the range [-7, +7] that is used to fine tune  $f_{BAUD}$

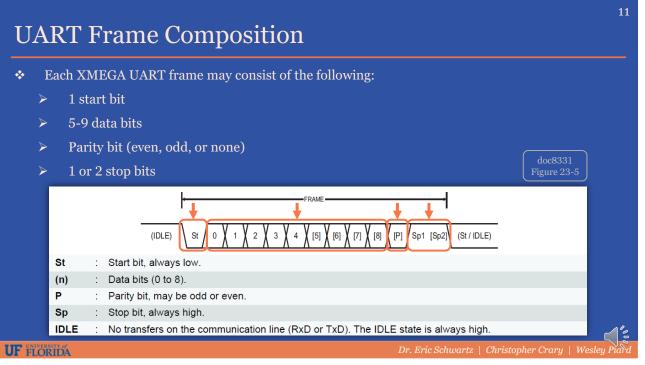

### Initializing the TxD Pin

- If the transmitter is to be utilized, the TxD pin must be configured as an output.

- Additionally, the initial output value for this pin should be high, such that it is initially in the idle state. This prevents any false start conditions from being interpreted by any UART connected to this pin.

- To do this, you configure the pin direction as output AFTER setting the pin's initial state to high.

#### Initializing the Baud Rate To configure the baud rate, the BSEL[11:0] and BSCALE[3:0] bits \* must be initialized. These bitfields are within the BAUDCTRLA and BAUDCTRLB • registers, as shown below. BAUDCTRLA Bit 6 5 4 3 2 1 0 +0x06 BSEL[7:0] BAUDCTRLB Bit 4 3 2 6 5 +0x07 BSCALE[3:0] BSEL[11:8] UF FLORIDA

### Initializing the Baud Rate - Example

As a simple example, we will determine the *BSEL* value that will yield a baud rate of approximately 9,600 bps. Assume *BSCALE* = 0 and  $f_{PER} = 2 MHz$ .

$$BSEL = \frac{f_{PER}}{2^{BSCALE} \cdot 16 f_{BAUD}} - 1$$

$$BSEL = \frac{2,000,000}{2^0 \cdot 16 \cdot 9,600} - 1$$

$$BSEL = 12.02 \approx 12$$

• If we plug *BSEL* = 12 back into this equation, we get

$$f_{BAUD}$$

= 9,615 bps

- ◆ This would be an error of about 0.16% which is generally acceptable.

- The amount of error that is acceptable is dependent on the application.

Testing should be performed to rule out the possibility of errors occurring.

| UF FLORIDA | Dr. Eric Schwartz | Christopher Crary | Wesley Pia |

|------------|-------------------|-------------------|------------|

|            |                   |                   |            |

17

#### 18 Initializing the Baud Rate - Example \* Since we determined *BSEL* = 12, and *BSCALE* = 0, we would configure the BAUDCTRL registers as follows: $\underline{BAUDCTRLA} = \underline{BSEL[7:0]} = \overline{12} = 0b0000\overline{1100}$ $\triangleright$ BAUDCTRLB = 0 $\triangleright$ BAUDCTRLA Bit 6 5 4 3 2 1 0 +0x06 BSEL[7:0] BAUDCTRLB Bit 4 3 2 6 5 +0x07 BSCALE[3:0] BSEL[11:8] UF FLORIDA

### Initializing the Operation Mode

The operation mode for a UART module is configured by the CMODE[1:0] bitfield.

| ✤ For | r this co | urse, we     | will gen  | erally us | se          |    |                     | doc8331<br>Table 23-7      |

|-------|-----------|--------------|-----------|-----------|-------------|----|---------------------|----------------------------|

| the   | asyncl    | hronou       | s mode,   | thus      | CMODE[1:    | 0] | Group configuration | Mode                       |

|       |           | 0] = 0b0     |           |           | 00          |    | ASYNCHRONOUS        | Asynchronous USART         |

|       | - L       |              |           |           | 01          |    | SYNCHRONOUS         | Synchronous USART          |

|       |           |              |           |           | 10          |    | IRCOM               | IRCOM <sup>(1)</sup>       |

|       |           |              |           |           | 11          |    | MSPI                | Master SPI <sup>(2)</sup>  |

| OTDI  |           |              |           |           |             |    |                     |                            |

| CTRL  | _         |              |           |           |             |    |                     |                            |

| Bit   | 7         | 6            | 5         | 4         | 3           | 2  | 1 0                 | doc8331                    |

|       | 7         | 6<br>DE[1:0] | 5<br>PMOD |           | 3<br>SBMODE | -  | 1 0<br>:HSIZE[2:0]  | doc8331<br>Section 23.15.5 |

| Initializ                | zing the                                     | Fram       | ie Fo   | rmat -  | - Par | ity Mo          | ode                   | 21                    |

|--------------------------|----------------------------------------------|------------|---------|---------|-------|-----------------|-----------------------|-----------------------|

| bitfield                 | rity mode, o<br>specifies wl<br>used, if any | hich type  |         | ity     |       |                 |                       | doc8331<br>Table 23-8 |

| 🔹 If parit               | y is enabled                                 | , the trai | nsmitte | r PMODE | [1:0] | Group cor       | nfiguration           | Parity Mode           |

|                          | comatically g                                | -          |         | nd oo   |       | DISA            | BLED                  | Disabled              |

| the par                  | ity of the da                                | ta bits w  | vithin  | 01      |       | -               | -                     | Reserved              |

| each fra                 | ame.                                         |            |         | 10      |       | EV              | ΈN                    | Enabled, even parity  |

|                          |                                              |            |         | 11      |       | OI              | DD                    | Enabled, odd parity   |

| CTRLC                    |                                              |            |         |         |       |                 |                       |                       |

| Bit 7                    | 6                                            | 5          | 4       | 3       | 2     | 1               | 0                     | doc8331               |

| +0x05                    | CMODE[1:0]                                   | PMOD       | E[1:0]  | SBMODE  |       | CHSIZE[2:0]     |                       | Section 23.15.5       |

| UF UNIVERSITY of FLORIDA |                                              |            |         |         | 1     | Dr. Eric Schwar | •tz   Chri <u>sto</u> |                       |

| 21                       |                                              |            |         |         |       |                 |                       |                       |

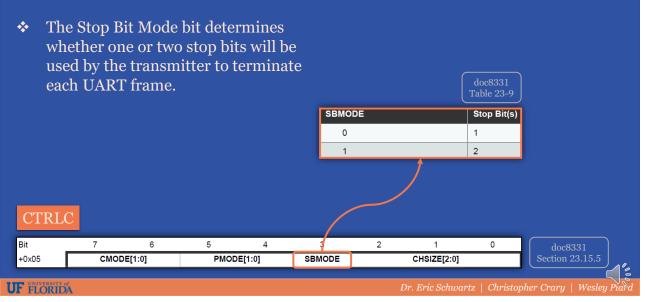

### Initializing the Frame Format – Stop Bit Mode

| ✤ The Character Size bitfield                     |             |                     | doc8331<br>Table 23-10 |

|---------------------------------------------------|-------------|---------------------|------------------------|

| determines the number of data bits                | CHSIZE[2:0] | Group configuration | Character size         |

| contained within each frame.                      | 000         | 5BIT                | 5-bit                  |

|                                                   | 001         | 6BIT                | 6-bit                  |

| <ul> <li>Note that the transmitter and</li> </ul> | 010         | 7BIT                | 7-bit                  |

| receiver must have the same                       | 011         | 8BIT                | 8-bit                  |

| configuration.                                    | 100         | _                   | Reserved               |

|                                                   | 101         | -                   | Reserved               |

|                                                   | 110         | -                   | Reserved               |

|                                                   | 111         | 9BIT                | 9-bit                  |

| CTRLC                                             |             |                     |                        |

| Bit 7 6 5 4                                       | 3 2         | 0                   | doc8331                |

| +0x05 CMODE[1:0] PMODE[1:0] SE                    | BMODE       | CHSIZE[2:0]         | Section 23.15.5        |

28

### UART Data Register

- The transmit data buffer register (TXB) and receive data buffer register (RXB) share the same I/O memory address, which is referred to as the UART data register (DATA).

- Data written to the DATA register goes to the TXB register to be transmitted.

- Data received by the receiver, which gets stored in the RXB register, can be accessed by reading the DATA register.

| DATA      |   |   |   |   |                  |   |                |                 |                            |

|-----------|---|---|---|---|------------------|---|----------------|-----------------|----------------------------|

| Bit       | 7 | 6 | 5 | 4 | 3                | 2 | 1              | 0               |                            |

| +0x00     |   |   |   |   | [[7:0]<br>[[7:0] |   |                |                 | doc8331<br>Section 23.15.1 |

| F FLORIDA | 4 |   |   |   |                  | I | Dr. Eric Schwo | urtz   Christop | oher Crary   Wesley        |

|           |   |   |   |   |                  |   |                |                 |                            |

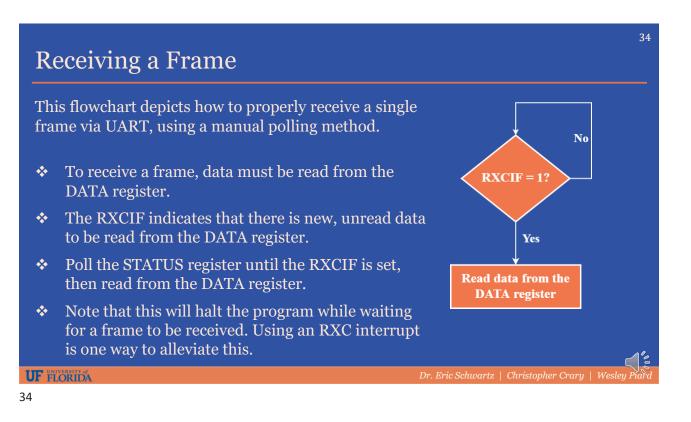

UART Status Register – Receive Complete Interrupt Flag

### ✤ RXCIF (Bit 7)

- > This flag is set when there are unread data in the receive buffer.

- It is cleared when the receive buffer is empty (i.e., does not contain any unread data).

- When interrupt-driven data reception is used, the receive complete interrupt routine **must** read the received data from the DATA register in order to clear RXCIF.

| STATU     | JS    |       |       |      |        |      |              |                 |                           |

|-----------|-------|-------|-------|------|--------|------|--------------|-----------------|---------------------------|

| Bit       | 7     | 6     | 5     | 4    | 3      | 2    | 1            | 0               | doc8331                   |

| +0x01     | RXCIF | TXCIF | DREIF | FERR | BUFOVF | PERR | -            | RXB8            | Section 23.15.2           |

| UF FLORID |       |       |       |      |        | L    | r. Eric Schw | artz   Christoj | pher Crary   Wesley Piard |

30

#### UART Status Register – Transmit Complete Interrupt Flag TXCIF (Bit 6) \* This flag is set when the entire frame in the transmit shift register $\geq$ has been shifted out and there are no new data in the transmit buffer. > It is automatically cleared when the transmit complete interrupt vector is executed. Alternatively, it can manually be cleared by writing a '1' to its bit $\geq$ location. **STATUS** Bit 7 6 5 4 3 2 1 0 +0x01 RXCIF TXCIF DREIF FERR BUFOVF PERR RXB8 UF FLORIDA

29

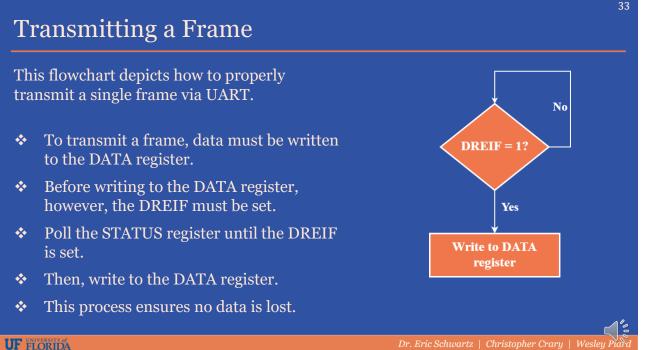

### UART Status Register – Data Register Empty Interrupt Flag

| * | DREIF | (Bit 5) |

|---|-------|---------|

| • | DIGLI | (Dit U) |

- > This flag indicates whether the transmit buffer (DATA) is ready to receive new data.

- This bit is one when the transmit buffer is empty and zero when the transmit buffer contains data to be transmitted that has not yet been moved into the shift register.

- Always write the DREIF bit to zero when writing the STATUS register. You will need to write to the STATUS register if you need to manually clear an interrupt flag.

- > DREIF is cleared by writing to the DATA register.

| STATU      | JS    |       |       |      |        |      |              |                 |                           |

|------------|-------|-------|-------|------|--------|------|--------------|-----------------|---------------------------|

| Bit        | 7     | 6     | 5     | 4    | 3      | 2    | 1            | 0               | doc8331                   |

| +0×01      | RXCIF | TXCIF | DREIF | FERR | BUFOVF | PERR | -            | RXB8            | Section 23.15.2           |

| UF FLORIDA | 4     |       |       |      |        | D    | r. Eric Schw | artz   Christoj | oher Crary   Wesley Piard |

### **Enabling UART Interrupts**

- Each of the three UART interrupts (RXC, TXC, and DRE) can be \* enabled with different priority levels, as per the PMIC.

- Each of these interrupts is triggered by its respective interrupt \* flag in the USART STATUS register (RXCIF, TXCIF, and DREIF).

| ; USART | C0 inter | rrupt vector                                                                                                       | rs | Interrupt leve | el configuration | Group configurat | ion | Description            |

|---------|----------|--------------------------------------------------------------------------------------------------------------------|----|----------------|------------------|------------------|-----|------------------------|

| .equ US | ARTCØ_RX | <c_vect 50<="" =="" td=""><td>0</td><td></td><td>00</td><td>OFF</td><td></td><td>Interrupt disabled.</td></c_vect> | 0  |                | 00               | OFF              |     | Interrupt disabled.    |

|         | _        | RE_vect = 52<br>KC vect = 54                                                                                       |    |                | 01               | LO               |     | Low-level interrupt    |

| .equ US | ARICO_IX | $C_vect = 5^2$                                                                                                     | ÷  |                | 10               | MED              |     | Medium-level interrupt |

|         |          |                                                                                                                    |    |                | 11               | н                |     | High-level interrupt   |

| CTRLA   |          |                                                                                                                    |    |                |                  |                  |     |                        |

|         | 7        | 6                                                                                                                  | 5  | 4              | 3                | 2 1              | 0   |                        |

| Bit     | 7        |                                                                                                                    | 5  | -              |                  |                  | -   | doc8331                |

31

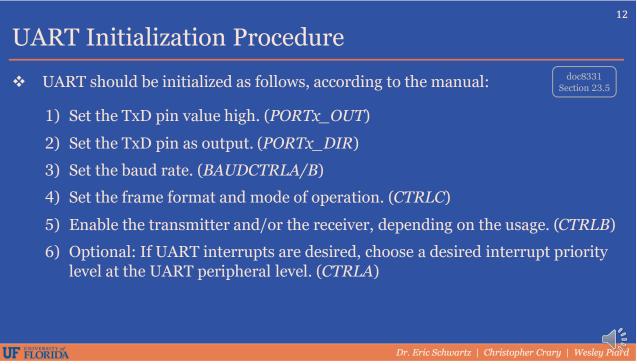

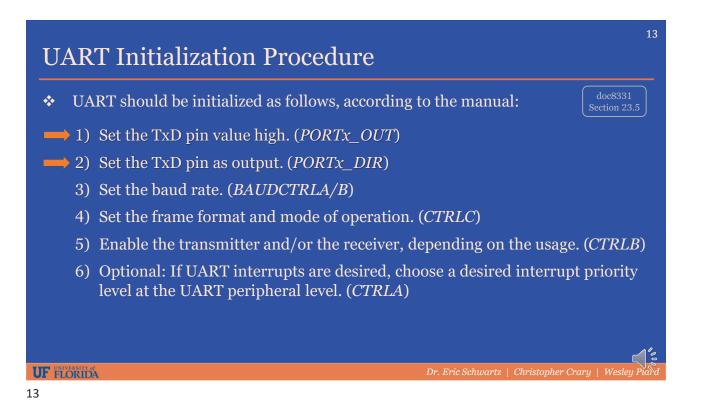

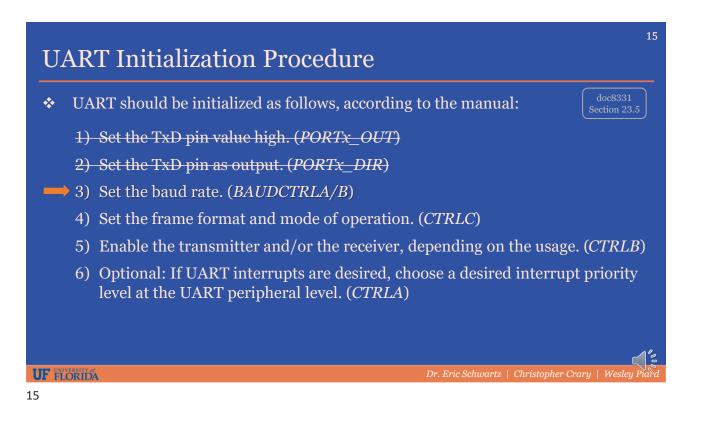

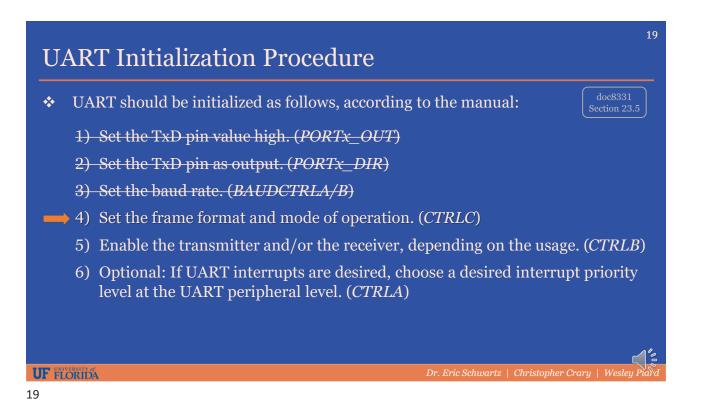

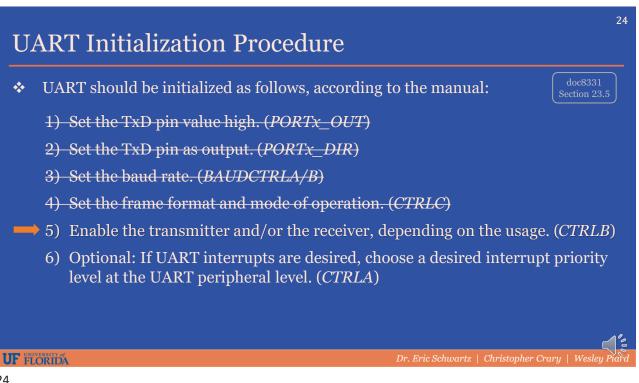

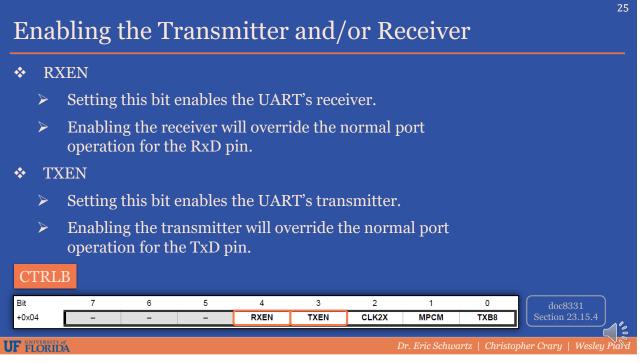

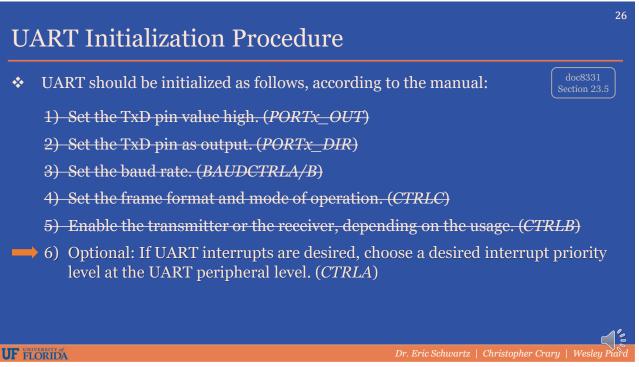

## 32 **UART** Initialization Procedure UART should be initialized as follows, according to the manual: \* 1) Set the TxD pin value high. (PORTx\_OUT) 2) Set the TxD pin as output. (PORTx DIR) 3) Set the baud rate. (BAUDCTRLA/B) 4) Set the frame format and mode of operation. (CTRLC) 5) Enable the transmitter and/or the receiver, depending on the usage. (CTRLB) 6) Optional: If UART interrupts are desired, choose a desired interrupt priority level at the UART peripheral level. (CTRLA) UF FLORIDA

#### **CA** FLU

33

### Conclusion

- The XMEGA's USART system can be set up quickly while maintaining flexibility.

- Section 23 of the XMEGA AU manual (doc8331) contains all the details that you may need to learn regarding the USART system.

- Section 33.2 of the ATxmega128A1U datasheet contains a collection of alternate pin function tables. This is where you should go to determine which physical pin(s) on the XMEGA are used for certain peripheral functions, e.g. UART Rx and Tx.

- This presentation only introduced the common features of the XMEGA's USART system. There are still some thing you will need to discover on your own.

UF FLORIDA

r. Eric Schwartz | Christopher Crary | Wesley Piard